圖1顯示了模擬I/O PAD模塊的傳統(tǒng)ESD方法。它由一個(gè)連接Vss到I/O PAD的二極管和連接I/O PAD模塊到Vdd的二極管以及在Vdd和Vss之間的電源/軌鉗位組成[1-5]。

IC設(shè)計(jì)人員之所以喜歡它,是因?yàn)檫@兩個(gè)二極管的設(shè)計(jì)容易實(shí)現(xiàn)且硅占用面積小,寄生電容相當(dāng)?shù)汀?/span>

圖1:應(yīng)用于許多I/O PAD模塊的傳統(tǒng)ESD方法:一個(gè)從Vss到I/O的二極管,另一個(gè)從I/O到Vdd的二極管。一個(gè)動力鉗用于1/2應(yīng)力組合。

對于敏感節(jié)點(diǎn),IC設(shè)計(jì)人員會在I/O與電路之間增加一個(gè)隔離電阻,以增加ESD設(shè)計(jì)窗口。如果功能電路無法處理靜電釋放(ESD)電流,則在隔離電阻后面添加一個(gè)次級鉗位(圖2)。

圖2:有時(shí),IC設(shè)計(jì)人員會在I/O PAD模塊和電路之間增加一個(gè)電阻,并在敏感電路前安放一個(gè)小的次級鉗位。這會增加ESD設(shè)計(jì)窗口。

這種簡單的方法存在多個(gè)問題,特別是高速接口的問題:

(1)隔離電阻嚴(yán)重影響高速運(yùn)行效果并增加了噪聲。

(2)ESD二極管可能會在信號PAD和電源線之間引入過多的寄生電容。

(3)由于PAD和Vdd之間的噪聲耦合或信號電壓可能高于參考Vdd電壓,也有可能是因?yàn)榕湫蛦栴},某些接口無法承受從I/O PAD模塊到Vdd的二極管帶來的電壓刺激。

(4)對于敏感節(jié)點(diǎn),預(yù)期ESD電流路徑上的總壓降可能高于功能電路的故障電壓[5]。

減少電容(問題2)并提高電壓容限(問題3)的簡單方法是串聯(lián)使用2個(gè)或更多個(gè)二極管。但是,這會導(dǎo)致在ESD應(yīng)力出現(xiàn)更高的電壓降,從而惡化問題4。2017年,提出了具有新型雙極概念的替代方案[6-7]。

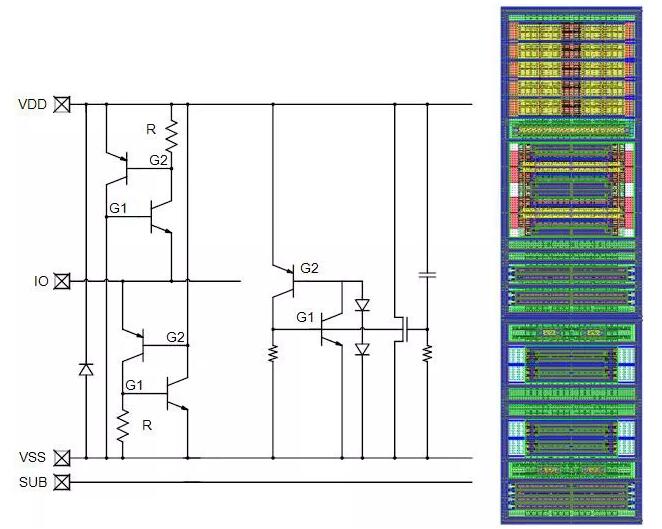

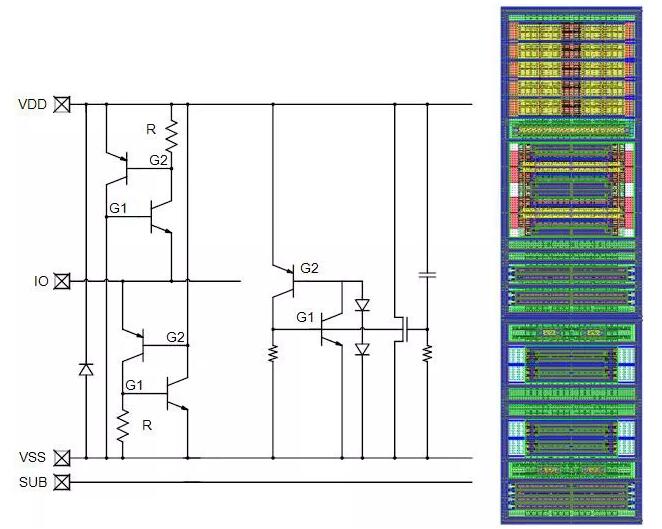

本文討論的項(xiàng)目中,IC設(shè)計(jì)人員使用局部保護(hù)鉗位概念代替了傳統(tǒng)的雙二極管ESD方法,如圖3所示。如果功能性操作不能承受二極管從“ IN”到Vdd,則可以將其取下。這對于安全故障,熱插拔,漏極開路輸出,冷備用輸入或耐壓過高的接口來說是很典型的現(xiàn)象[8]。

圖3:采用局部鉗位ESD保護(hù)的簡化電路原理圖。如果需要進(jìn)行功能操作,則可以去除IN和Vdd之間的二極管。在某些情況下,Vdd和“ IN”之間會再添加一個(gè)鉗位。

局部鉗位方法具有很多優(yōu)點(diǎn):

(1)減少對總線電阻的依賴

(2)ESD條件下的壓降大大降低,而無需隔離電阻,非常適合敏感節(jié)點(diǎn)。

(3)為減少寄生電容提供了不同的選項(xiàng)(請參見下面的案例研究)

(4)可以分別針對每個(gè)I/O PAD進(jìn)行優(yōu)化。例如: 一些PAD可能需要更高的ESD耐受性,否則無法承受I/O和Vdd之間二極管的放電。

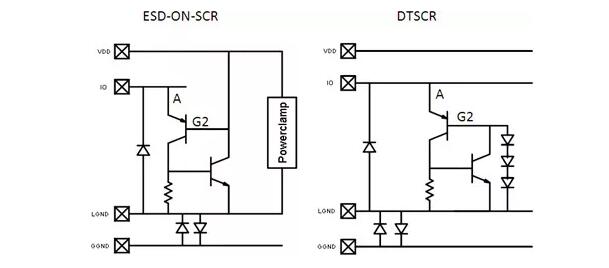

下面的案例研究總結(jié)了幾種具有(超)低寄生電容的局部鉗位方法,以保護(hù)從28nm CMOS到7nm FinFET各類的高速SerDes接口。在案例研究中使用了基于SCR的不同類型的局部鉗位(圖4)。二極管觸發(fā)式SCR和ESD-on-SCR以前用于保護(hù)無線LNA接口[9]。

圖4:案例研究中使用的兩個(gè)ESD保護(hù)夾。一旦IO電平將二極管壓降(Anode-G2)升高到高于Vdd電壓,就會觸發(fā)Sofics ESD-on-SCR。一旦AnodeG2和觸發(fā)二極管被正向偏置,則Sofics DTSCR打開。

1.FPGA 28nm, 28Gbps SerDes

臺積電(TSMC)28nm中的一系列*FPGA產(chǎn)品,客戶需要定制的ESD保護(hù)單元。28Gbps SerDes接口需要以下規(guī)格:

-寄生電容遠(yuǎn)低于100fF。

-ESD等級:> 1kV HBM;> 250V CDM

選擇了Sofics DTSCR鉗位的縮小版本作為Tx和Rx接口的本地保護(hù)。在隔離電阻后面增加了一個(gè)次級本地CDM鉗位,以保護(hù)Rx情況下的薄柵極氧化物(圖5)。DTSCR,反向二極管和金屬連接的寄生電容保持在80fF以下。

圖5:28Gbps SerDes Rx(輸入)階段的示意圖,顯示了用于增強(qiáng)CDM保護(hù)的DTSCR本地鉗位和二級保護(hù)階段。

為了滿足S11–回波損耗規(guī)范,在DTSCR上串聯(lián)了一個(gè)電感器(圖6)。符合包括CDM在內(nèi)的所有規(guī)范。FPGA器件以4.5A的峰值電流達(dá)到300V以上。所有分析結(jié)果均已在IEW 2011活動中展示[10]。

圖6:為了滿足S11規(guī)范,在DTSCR上串聯(lián)了一個(gè)電感器。線圈降低了10 GHz和20 GHz時(shí)的S11峰值。

2.通用SerDes 16nm,28Gbps

具有16納米制程的28 Gbps SerDes的高速(數(shù)據(jù)中心)通信芯片需要定制的ESD保護(hù)方案。

本地ESD鉗位必須滿足這些要求:

-在ESD應(yīng)力低于3.3V時(shí)具有故障電壓的敏感薄氧化物0.8V核心晶體管的保護(hù)

-低泄漏ESD鉗位,在高溫(125°C)下低于10nA

-小硅片占用空間,可在同一通信芯片上啟用多個(gè)通道

-無電阻

- > 2kV HBM

-最大ESD結(jié)電容為100fF

圖7:Tx接口的差分對的保護(hù)概念的示意圖。在差分對的兩個(gè)路徑上都添加了一個(gè)本地鉗位和并聯(lián)反向二極管。

基于對TSMC16nm FinFET技術(shù)的芯片進(jìn)行的廣泛分析,選擇了ESD-on-SCR概念作為本地鉗位器件。TLP數(shù)據(jù)如圖8所示。

在小于1.000um2的面積內(nèi)保護(hù)2安培以上的薄氧化物器件。高溫下的泄漏約為1nA。

圖8:用作本地鉗位器件的SCR上ESD器件的TLP測量。在達(dá)到薄氧化物晶體管的故障電壓之前,器件達(dá)到2A以上。

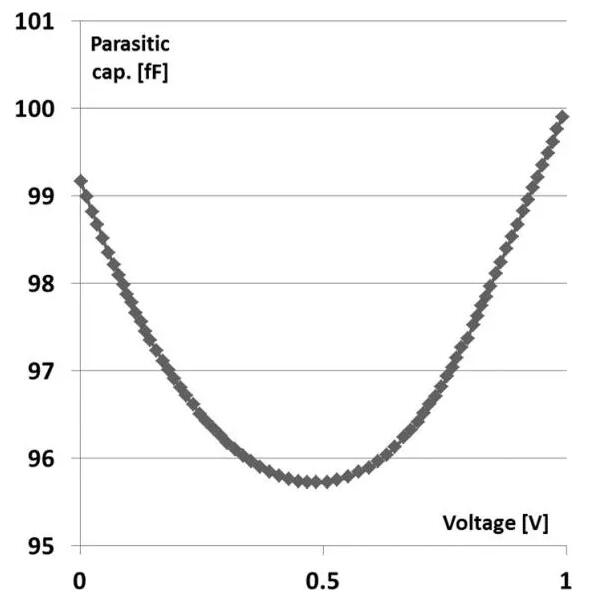

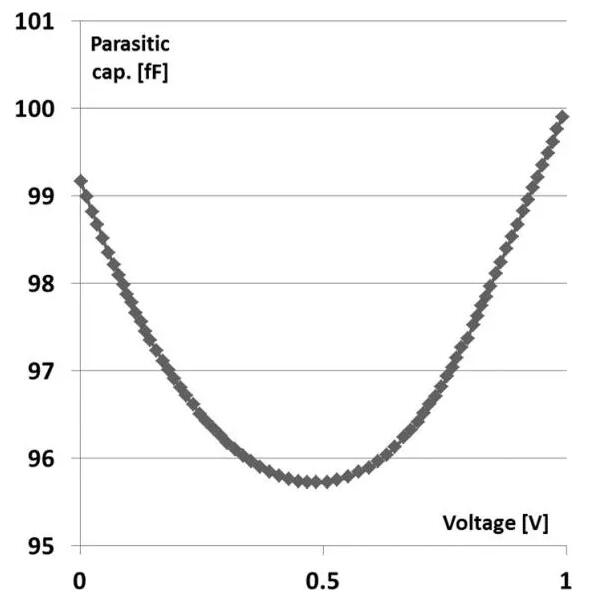

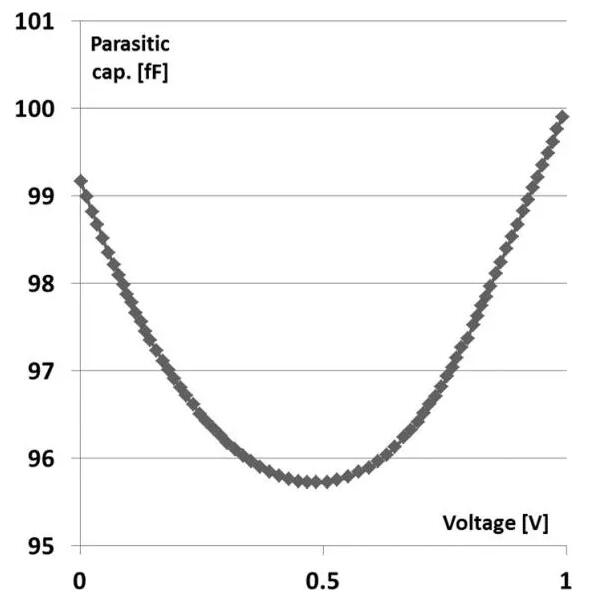

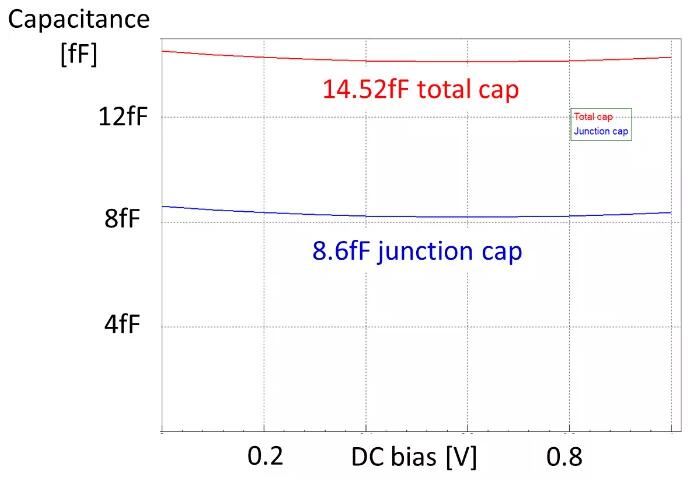

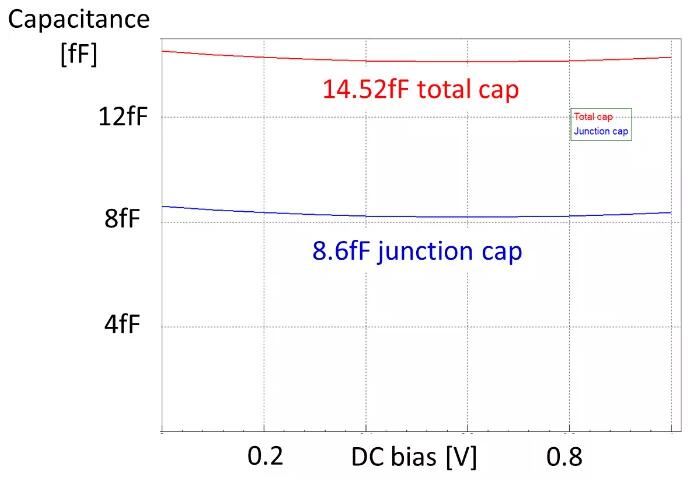

圖9:SCR上ESD的電容仿真(Spice)。在PAD的電壓范圍內(nèi),電容均保持在100fF的目標(biāo)電平以下。

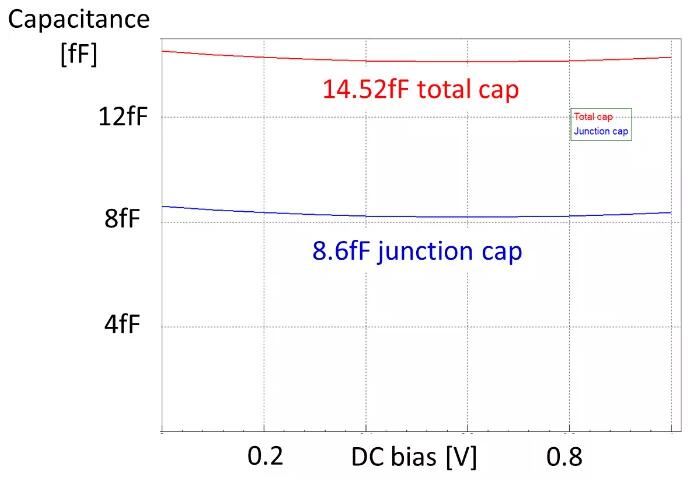

為了確保ESD保護(hù)鉗位不影響高速SerDes的運(yùn)行,在PAD電壓上模擬了寄生結(jié)電容,如圖9所示。使用了基于二極管結(jié)的等效模型來模擬靜電保護(hù)單元的電容負(fù)載。

3.硅光子學(xué)28nm,28Gbps

幾家從事新型光收發(fā)器工作的公司聯(lián)系我們尋求支持。對于常規(guī)的低速I/O(1.8V),鑄造廠提供的模擬/數(shù)字I/O庫已足夠。這些PAD的ESD要求為2kV HBM。

另一方面,代工廠庫中的模擬I/O為高速接口引入了過多的寄生電容。設(shè)計(jì)人員要求將ESD的總電容減小到15fF以下。

28nm CMOS SoC與硅光子器件共同封裝在共享/混合集成封裝中(圖10)。由于這種倒裝芯片組裝是在ESD控制的環(huán)境中進(jìn)行的,因此ESD保護(hù)級別可以降低至200V HBM,而不會影響成品率。

圖10 :(示例)使用倒裝芯片鍵合工藝將電子IC(驅(qū)動器)封裝在硅光子器件上(?IOP 2016 [11])。

圖11:在硅光子SerDes接口中使用的簡化的Tx /輸出電路。

28Gbps接口使用差分對概念,如圖11所示。使用0.9V核心晶體管創(chuàng)建1V功能電路,以確保可以達(dá)到開關(guān)速度。但是,這些晶體管將Rx,Tx信號的可用ESD設(shè)計(jì)窗口減小到4V。

ESD保護(hù)的其他要求包括低漏電操作和小硅面積。

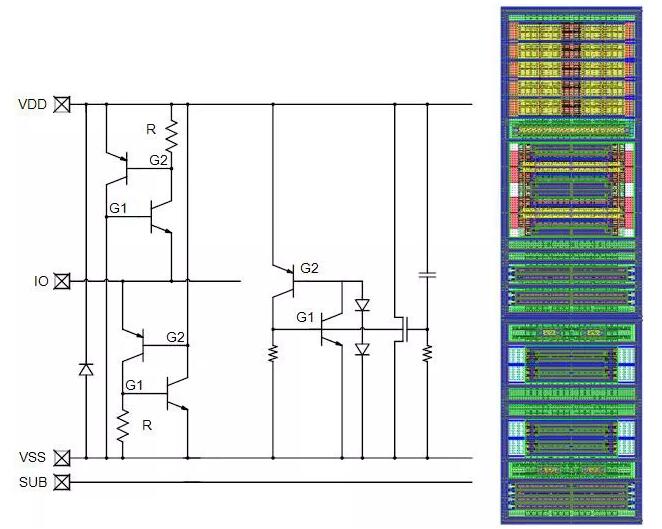

ESD保護(hù)設(shè)計(jì)包括完整的本地保護(hù)鉗位概念,如圖12所示。集成了1V電源鉗位,以確保所有應(yīng)力情況都可以在接口處進(jìn)行本地處理,并消除了母線電阻的影響。整個(gè)鉗位結(jié)構(gòu)與基板隔離,以減少來自襯底的噪聲,這些噪聲可能來自芯片上與之較遠(yuǎn)的數(shù)字電路。

圖12:SerDes電路的Rx和Tx節(jié)點(diǎn)的完整本地保護(hù)方法的示意圖(左)。基于SCR上的ESD器件。基于SCR的1V電源鉗夾集成在同一布局中(右)。ESD的總面積為683.75um2。

I/O PAD模塊上的總寄生電容包括不同方面。結(jié)電容可以很容易地從代工廠提供的二極管Spice模型中得出。本地ESD鉗位的金屬連接會增加大量電容。寄生金屬電容可以從PEX提取中得出。減小金屬連接的寬度可以減小電容,但也會降低線路的穩(wěn)定性。最小金屬寬度是由我們通過對不同弄金屬實(shí)施ESD應(yīng)力得出的。

當(dāng)客戶要求使用超低電容(遠(yuǎn)低于100fF)的ESD保護(hù)時(shí),PEX提取中將包括Metal dummy部分。

通過迭代過程(布局,PEX提取),ESD鉗位電路的總寄生電容減小至小于15fF。下圖將顯示此過程中的不同步驟。下圖(圖13)顯示了電容值與PAD上偏置電壓的關(guān)系。

必須減小對地的寄生電容,以防止高頻信號分流到地。

公式1:電容電抗Xc(以歐姆為單位)與信號頻率(f)和電容(C)成反比

對于高頻(> 50 Ghz),寄生電容表現(xiàn)為對地的電阻。該阻抗必須足夠高。15 fF的電容在50 GHz時(shí)的電阻約為200歐姆。

在迭代過程中,為了減少金屬連接對寄生電容的影響,使用了一些規(guī)則

-移除不必要的過孔連接

-盡可能減少金屬1,僅將其放在連接擴(kuò)散區(qū)的頂部。

-防止金屬層1穿過結(jié)區(qū)。

-垂直(向上)連接

即使通過以上方法降低寄生電容,在*節(jié)點(diǎn)上仍有42%的寄生電容與金屬連接有關(guān)。

圖13:I / O電壓上的寄生電容(僅總電容和結(jié)電容)。

使用HBM ESD應(yīng)力的瞬態(tài)Spice模擬,將圖12的局部鉗位方法與其他2個(gè)概念進(jìn)行了比較

-概念1:建議的局部鉗位

-概念2:Foundry提供的I/O PAD模塊(雙二極管和Foundry建議的核心功率鉗位)

-概念3:雙二極管與Sofics 1V核心保護(hù)鉗位組合

從圖14可以清楚地看到,概念2和3產(chǎn)生的壓降遠(yuǎn)高于基于薄氧化物晶體管[12]的敏感電路的故障電壓(4V)[12]。

圖14:HBM應(yīng)力下的瞬態(tài)Spice模擬。比較了3個(gè)概念,以驗(yàn)證在ESD應(yīng)力期間敏感節(jié)點(diǎn)上的電壓降保持在最大4V以下。只有建議的局部鉗位才能使ESD應(yīng)力低于4V。使用1kV HBM應(yīng)力和ESD器件縮放至1kV穩(wěn)健性進(jìn)行了比較。使用組合的NPN/PNP模型模擬SCR局部鉗位的驟回。

4.硅光子7nm FinFET

為了進(jìn)一步增加光互連的帶寬(超過56 Gbps),我們的客戶采用了TSMC 7nm FinFET技術(shù)。

所提出的解決方案類似于圖12。創(chuàng)建了兩種版本的ESD保護(hù),一種具有50fF的寄生電容,另一種具有15fF以下的小電容。在論文中,將包括這些案例研究。

臺積電(TSMC)的7納米FinFET工藝的初步測試表明,SCR上的ESD本地鉗位電路具有預(yù)期的效果(圖15)。

在7nm技術(shù)中,內(nèi)核晶體管(柵極到源極和漏極到源極)的故障電壓約為3V。幸運(yùn)的是,在許多SerDes應(yīng)用中,由于其他晶體管串聯(lián)在一起,會有更多的余量(圖11)。根據(jù)電路原理,這些電路的故障電壓約為4-5V。

7nm ESD鉗位已集成到2個(gè)用于高速接口的設(shè)計(jì)中。在撰寫本文時(shí),這些產(chǎn)品樣本尚未到位,因此CDM數(shù)據(jù)尚不可用。

圖15:基于TSMC 7nm技術(shù)的ESD-on-SCR概念的TLP分析。保護(hù)敏感的內(nèi)核晶體管。這種用于2kV HBM性能的參考器件已按比例縮小到15fF和50fF版本,以保護(hù)高速SerDes。

總結(jié)

用于模擬I/O PAD模塊的傳統(tǒng)“雙二極管” ESD保護(hù)概念在保護(hù)*CMOS和FinFET節(jié)點(diǎn)中的高速SerDes接口時(shí)遇到了問題。二極管,總線電阻和功率鉗位上的總壓降很容易超過核心晶體管的故障電壓。此外,“二極管向上”增加了限制因素。

這項(xiàng)工作顯示了幾個(gè)案例研究,其中雙二極管概念被替換為本地ESD保護(hù)鉗位。

基于專有的二極管觸發(fā)和ESD-on-SCR器件的I/O PAD模塊。本地鉗位降低了總線電阻的依賴性,降低了鉗位電壓,并允許分別優(yōu)化每個(gè)模擬I/O。此外,這些案例表明,可以創(chuàng)建具有非常低的寄生電容和較小的硅面積的ESD保護(hù)。

數(shù)據(jù)基于*CMOS和FinFET節(jié)點(diǎn)上的專用ESD測試芯片。這項(xiàng)工作中的模擬I/O被20多家公司用于保護(hù)28nm CMOS,16nm/12nm和7nm FinFET技術(shù)的高速SerDes接口。

免責(zé)聲明:本文轉(zhuǎn)載自“IP與SOC設(shè)計(jì)”,支持保護(hù)知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。